# 基于创新能力培养的 FPGA 应用设计实验教学探索

唐志辉<sup>\*</sup>, 黄环, 陈彦芳, 陈延金, 李泽轩, 郑志伟

东莞城市学院 城建与智造学院, 广东 东莞 523419

DOI: 10.61369/ETR.2025470021

**摘要 :** 针对FPGA(现场可编程门阵列)实验教学具有较强的综合性、工程性、实践性以及教学中存在的问题,采用PBL(问题导向)与线上线下相结合的教学模式,以学生主动学习为中心,理论与实际应用相融合。在不同教学阶段采用不同的方案设计同一电路,不断完善电路功能与性能。以序列检测器设计为例,说明了基本电路功能设计、基于状态机设计优化电路性能、调用IP核设计更接近实际应用,增强了实验的扩展性与创新性,有效提升了学生的工程实践能力,取得了良好的教学效果<sup>[1,2,3]</sup>。

**关键词 :** FPGA; 实验教学; 线上线下; 问题导向; 电路功能与性能; 序列检测器

## Application of PBL, BL and CB Combined Teaching Method in FPGA Application Design Experiments

Tang Zhihui, Huang Huan, Chen Yanfang, Chen Yanjin, Li Zexuan, Zheng Zhiwei

School of Urban Construction and Intelligent Manufacturing, Dongguan University, Dongguan, Guangdong 523419

**Abstract :** Addressing the comprehensive, engineering-oriented, and practical nature of FPGA (Field-Programmable Gate Array) experimental teaching, as well as the issues present in the teaching process, a teaching model that combines PBL(Problem-Based Learning) with both online and offline methods has been adopted. This model emphasizes student-centered active learning and the integration of theory with practical application. At different teaching stages, various design approaches are employed to design the same circuit, continuously refining its functionality and performance. Using the design of a sequence detector as an example, this method illustrates the basic circuit function design, performance optimization based on state machine design, and the use of IP cores to more closely align with real-world applications. This approach enhances the expansibility and innovation of experiments, effectively improving students' engineering practice capabilities and achieving positive teaching results<sup>[1,2,3]</sup>.

**Keywords :** FPGA; experimental teaching; online and offline; problem-based learning; circuit functionality and performance; sequence detector

## 引言

随着FPGA(现场可编程门阵列, Field Programmable gate Array)结构和功能的不断完善,各种功能的IP核(知识产权核, Intellectual Property Core)嵌入到FPGA芯片中,使用FPGA代替ASIC(专用集成电路, Application Specific Integrated Circuit)进行电路设计成为集成电路设计一个重要发展方向。目前,我国的集成电路产业掌握核“芯”技术刻不容缓,很多高校开设了基于FPGA的EDA技术课程,尤其是电子科学与技术专业,更是以FPGA应用设计作为核心教学内容<sup>[1,4]</sup>。

## 一、课程特色与教学存在的问题

系统的程序实现。

### (一) 课程特色

FPGA应用技术涉及的知识点较多,主要包含四大模块<sup>[5,6]</sup>: FPGA的结构及工作原理、EDA软件工具、硬件描述语言、数字

课程具有较强的工程性、综合性、实践性。FPGA具有的可重复编程的优点,非常适合在实验室中进行程序修改,可以根据需求不断地进行调整。实验教学不仅加深对理论的理解,而且富有挑战性和开拓性,能培养学生发现问题、分析问题、解决问题

基金项目:

东莞城市学院教学质量工程项目:线上线下混合式一流本科课程《EDA技术基础》(2023ylkc003); (2023zlgc006);

2022年度广东省本科高校教学质量与教学改革项目:先进制造实验教学示范中心,粤教高函[2023]4号;

作者简介:唐志辉,硕士,副教授,研究方向为电路设计、仪器仪表。Tel:13790130476; E-mail:tangzhihui@163.com。

通讯作者:唐志辉,硕士,副教授,研究方向为电路设计、仪器仪表。Tel:13790130476; E-mail:tangzhihui@163.com。

的探索精神和创新能力<sup>[10,12]</sup>。

## (二) 教学存在的问题

我校设置课程总学时为48课时，其中理论课时28，实验课时20。教学存在以下问题：

无论是理论还是实验，存在教学课时少，教学内容多和难度较大的问题。部分学生反映理论课跟不上，实验完成不了；

把实验教学安排在理论教学完成以后，效果不好。长时间的集中理论教学，由于理论知识比较枯燥，学生积极性不高，即使课堂能听懂，但没有通过实践强化，理解不深刻，做实验的时候感觉困难，学生对的Quartus II软件操作、状态机设计方法、IP核的调用等不熟悉，实验的扩展及创新性不够。

## 二、FPGA实验教学改革思路

### (一) 基于PBL的教学

通过在问题情景中设置学习的主要内容，引导学生在分析问题的同时掌握相应的知识点<sup>[7,8]</sup>。

具体做法是：

实验课前，采用提问的方式引导学生思考设计的关键点，并发布实验解决方案微视频。对于复杂的设计方案允许2~3人一组，学生们在问题的引导下一起讨论和交流，构建“协作学习”环境。

实验课中，采取翻转课堂，重点解决课前无法完成的疑难问题，并完成基于实验箱的硬件测试。

实验课后，提问引导学生思考：实验存在的问题及解决方案；设计还可以从哪些方面进行完善；设计的电路可以应用到哪些系统中、应如何修改等。以项目为导向，培养学生的工程实践能力和创新精神。

### (二) 线上、线下混合式教学

针对实验工作量与难度大，难以在2个课时内完成的情况，借助“超星学习通”APP与企业微信，进行线上线下混合式教学<sup>[3,9]</sup>。

实验课前，提前约2天线上发布实验微视频及相关学习资料，要求学生自学后尝试完成程序设计、时序仿真及引脚锁定，实验课前采用问卷调查对学生自学情况摸底。

课内针对重点及难点进行线下讲解、答疑，由于课前的充分准备，学生在课内有充足的时间解决课前存在的问题，并在实验箱上完成实验的最后一步硬件测试。

实验课后，引导学生进一步完善设计方案，把设计的电路应用到实际系统中，采取线上辅导，学生组队完成。

## 三、教学法的具体实施及成效

以设计序列检测器实验为例，阐述实施方法及效果。

### (一) 第一次实验<sup>[2,5]</sup>

实验前，让学生根据已学理论自主设计，引导问题有：<sup>[11]</sup>

(1) 电路有哪些输入、输出端口？在实体中定义时，各端口的采用什么数据类型，其长度为多少位？

(2) 在程序中如何记录连续正确的位数？

(3) 硬件测试时，如何给输入信号，又如何显示输出信号？

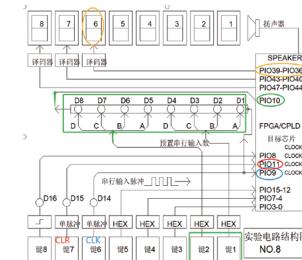

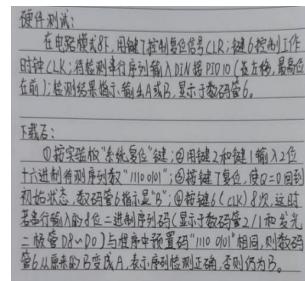

要求学生学习微视频后，完成程序设计、仿真、引脚锁定等工作。实验课内采取共同问题课堂讲解，个别问题单独答疑。从课前、课后的摸底问卷（图3、图4）可以看出，课前约50%的学生表示能独立完成，课后实验完成率为100%，大幅提升了学习效果。图1、图2是学生基于康芯GW48 EDA实验箱的硬件测试方案与硬件测试方法说明<sup>[13]</sup>。

图1 硬件测试方案

图2 硬件测试说明

图3 课前摸底问卷结果

图4 课后摸底问卷结果

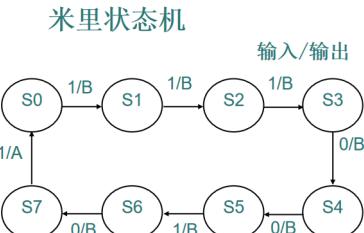

### (二) 第二次实验

在常用数字逻辑电路的VHDL描述及状态机的学习之后，实验前的引导问题有：

(1) 电路是否可以采用状态机设计方法？该采用哪种状态机？

- (2) 电路需要定义多少个状态? 状态转换图如何画?

- (3) 用仿真结果对比分析, 没采用状态机与基于状态机的设计有何不同效果<sup>[3,6]</sup>?

- (4) 用仿真结果对比分析, 采用双进程状态机与单进程状态机设计有何不同效果?

让学生思考这些问题之后在线上发布微视频, 讲述在第一次实验程序的基础上增加状态机的解决方案, 并阐明采用双进程状态机与单进程状态机设计, 两者程序的区别, 以及如何设置仿真输入信号, 才能在仿真结果中看到不同设计方法实现的电路功能与性能的差别<sup>[4,11]</sup>。状态转换图如图5所示。

图5 状态转换图

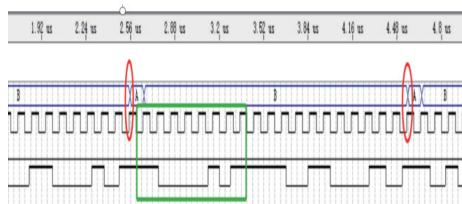

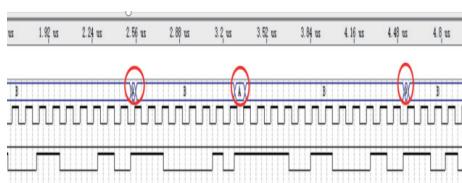

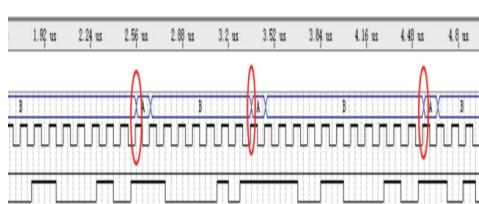

下面是学生对相同输入信号, 采用不同设计方法的仿真的结果(图6~图8)及结论(图9、图10)。

图6 非状态机程序仿真结果

图7 双进程状态机程序仿真结果

图8 单进程状态机程序仿真结果

**双进程状态机与单进程状态机的比较:**

1.产生输出的时间间隔差异

双进程状态机的输出信号是由组合逻辑产生的, 组合逻辑没有时钟的限制, 代码是即时进行的, 输出在当前状态一出现就产生。

单进程的紫码扫描与单时钟进程混合为一个进程, 所以输出的产生也要受时钟的约束, 只有在时钟有效边沿到达时才能有机会完成输出赋值。

2.抑制抖动能力的差异

双进程状态机的输出信号是由组合逻辑产生的, 组合逻辑存在竞争冒险问题, 所以输出信号会受到抖动影响。

单进程状态机的输出信号的产生是在时钟的统一触发下产生的, 相当于有一个锁存器, 因而输出能够有效避免了竞争冒险, 就消除了波形抖动。

图9 双进程与单进程状态机结果的比较

状态机设计方法与非状态机设计方法仿真结果的比较

第一次实验, 选择非状态机, 流程是这样的: 首先检测到你进来的正确数据和检测到Q=0(应该是在波形图第1位), 这样在检测到一个正确的以后, Q=0, 下一个时钟上升沿来时, 不能开始新一轮的检测, Q需要是回到0才能开始。这就使得当输入信号出现连续多个正确码时, 只能检测到第一个正确码, 所以只出现了第一次。

第二次实验, 选择状态机的设计流程, 流程是这样的: 检测到正确的正确数据, 而用状态机检测到Q=0, 检测到一个正确的码以后, Q=0, S=0, 回到初始状态, 下一个时钟上升沿来时, 开始新一轮的周期检测。避免了对连续出现的正确码的误判。

结论: 状态机的设计具有更高的可靠性。

图10 状态机与非状态机设计方法比较

### (三) 第三次实验

安排在复杂数字系统设计及IP核的学习之后, 实验前提出引导问题如下<sup>[1,12]</sup>:

(1) 大多数实际情况是需要检测一组或多组串行二进制码, 待检测码远远超过8位, 如何在不改变实验箱的硬件配置情况下, 通过修改程序来实现?

(2) 是否可以通过调用IP核ROM, 提前把多位待检测码存入? 如可以, 如何设置ROM的参数?

(3) 调用IP核ROM, 是否需采用层次电路设计? 如需要, 程序应包含哪些模块?

(4) 硬件测试方法与之前比有何不同? 可以不采用手动时钟吗? 如可以, 应设置时钟周期至少为多少, 才能清楚的看出测试结果的变化?

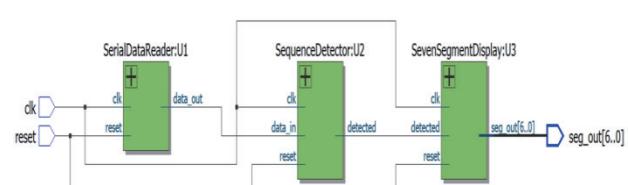

之后在线上发布调用IP核ROM的微视频及具体设计任务如下:

(1) 每个同学需要检测的数据是学号后2位作为16进制转换为8位二进制数(比如: 15号同学其检测码为: 00010101)。

(2) 通过ROM模块存放待检测的串行数据流, 要求: 每个存储单元存储1bit数据, 共有32个数据(数据可随机)。

(3) 设计串行数据读出模块, 实现从ROM中循环读出数据, 生成与时钟clk同步的串行数据流。

(4) 设计序列检测模块。画出序列检测状态图, 编写基于状态机的程序。

(5) 设计数码管显示模块, 驱动数码管显示A或B。

(6) 设计顶层模块, 下层包含串行数据读出模块, 序列检测模块, 数码管显示模块。

(7) 对以上各模块建立仿真输入文件, 并完成各模块仿真。

(8) 利用实验箱设计硬件测试电路, 完成引脚锁定、下载、观察测试现象。

通过提示问题的引导、学习微视频、线上答疑、课堂指导, 超过70%的学生可以按照设计任务要求完成基于ROM的设计, 对有困难的学生允许组队完成。

顶层模块RTL电路如图11所示。

图11 顶层模块 RTL 电路图

三次实验之后，向学生提出，在实际应用中待检测码有时是随机出现的，无法在 ROM 中提前设置，是否可以通过调用 IP 核 RAM 来实现？如可以，程序该如何修改？引导学生思考序列检测器在实践中的有哪些应用，并以项目为导向，培养学生解决复杂工程问题及知识综合应用的能力<sup>[8,10]</sup>。

穿理论教学，顺序渐进，高度融合理论与实践，解决了学生对理论知识理解不深刻、实验课时少等问题，有效提升了学生的参与度，拓展了实验的广度和深度，提高了教学质量，在以后的教学中可精选更多接地气的案例，注重数据采集、控制器等方面，进一步完善教学内容<sup>[7-10]</sup>。

## 四、总结

基于问题导向的线上线下混合式 FPGA 实验教学，将实验贯穿理论教学，顺序渐进，高度融合理论与实践，解决了学生对理论知识理解不深刻、实验课时少等问题，有效提升了学生的参与度，拓展了实验的广度和深度，提高了教学质量，在以后的教学中可精选更多接地气的案例，注重数据采集、控制器等方面，进一步完善教学内容<sup>[7-10]</sup>。

## 参考文献

- [1] 华一村, 曹源, 张义红等. 应用型创新人才培养的 FPGA 实验教学研究 [J]. 实验室研究与探索, 2019, 38(8):184-188.

- [2] 郝彦爽, 林颖, 韩守梅. 基于 FPGA 的数字电子技术实验案例设计 [J]. 实验室科学, 2021, 24(03): 1-3.

- [3] 田莹, 卢金玉, 刘宴涛. 基于 Matlab/Simulink 的通信原理虚拟仿真实验教学方法研究 [J]. 现代电子技术, 2015, 38(14):28-31.DOI:10.16652/j.issn.1004-373x.2015.14.023.

- [4] 薛浪, 曾庆立, 周佳凯, 等. 基于 FPGA 的直线检测设计与实现 [J]. 现代电子技术, 2025, 48(09):43-48.DOI:10.16652/j.issn.1004-373x.2025.09.007.

- [5] 张博, 张文爱.《EDA 技术与 FPGA 应用设计》(第 3 版)[M]. 北京: 电子工业出版社, 2023.

- [6] 张瑾, 李泽光, 韩睿, 孙芹芝等.《EDA 技术及应用》(第 2 版)[M]. 北京: 清华大学出版社, 2021.

- [7] 王彩凤, 李志远, 高海阔, 毛国明等. 基于 PBL 教学法的电子设计自动化混合式教学模式改革研究与实践 [J]. 创新创业理论研究与实践, 2024(12): 170-173.

- [8] 文进, 顾少轩. 新工科背景下以问题驱动的混合式教学设计 [J]. 高教学刊, 2021(22):122-125.

- [9] 汪红兵. 基于问题导向的探究式线上线下混合教学模式应用研究 [J]. 科技与创新, 2021(13):29-31.

- [10] 傅莉. PBL 模式下的 EDA 技术课程教学改革研究 [J]. 中国现代教育装备, 2021(19): 124-126.

- [11] Shi J, Deng C. Digital circuit experiment system based on FPGA[C]// International Conference on E-health Networking. 2010.

- [12] Benkrid K, Clayton T. Digital Hardware Design Teaching: An Alternative Approach[M]. ACM, 2012.

- [13] 杭州康芯电子有限公司, GW48PK3\_EDA 实验系统 [EB/OL]. [http://www.kx-soc.com/kangxin1/wap\\_pro/3566328.html](http://www.kx-soc.com/kangxin1/wap_pro/3566328.html), 2013.09.